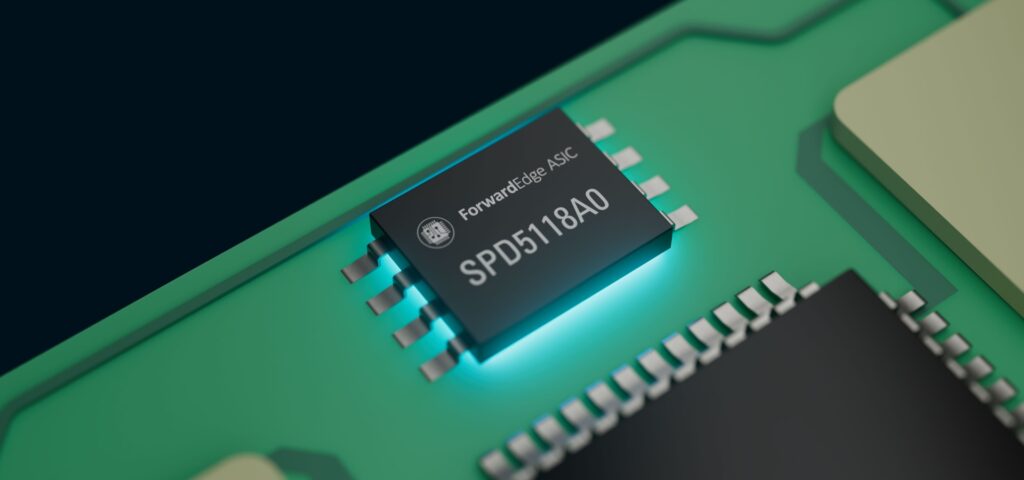

Vertically integrated Design team with decades of proven experience. ForwardEdge is an integrated ASIC design group based in St. Paul, Minnesota. Our engineers have worked together for over 30 years, covering every design phase from requirements to high volume manufacturing (HVM) in a variety commercial, Aerospace and Defense markets. All development is done in the U.S., with 100% domestic traceability and a reliable, secure supply chain. We pride ourselves in achieving an 85% first pass silicon success rate.

Capabilities and

Proven Areas of Expertise

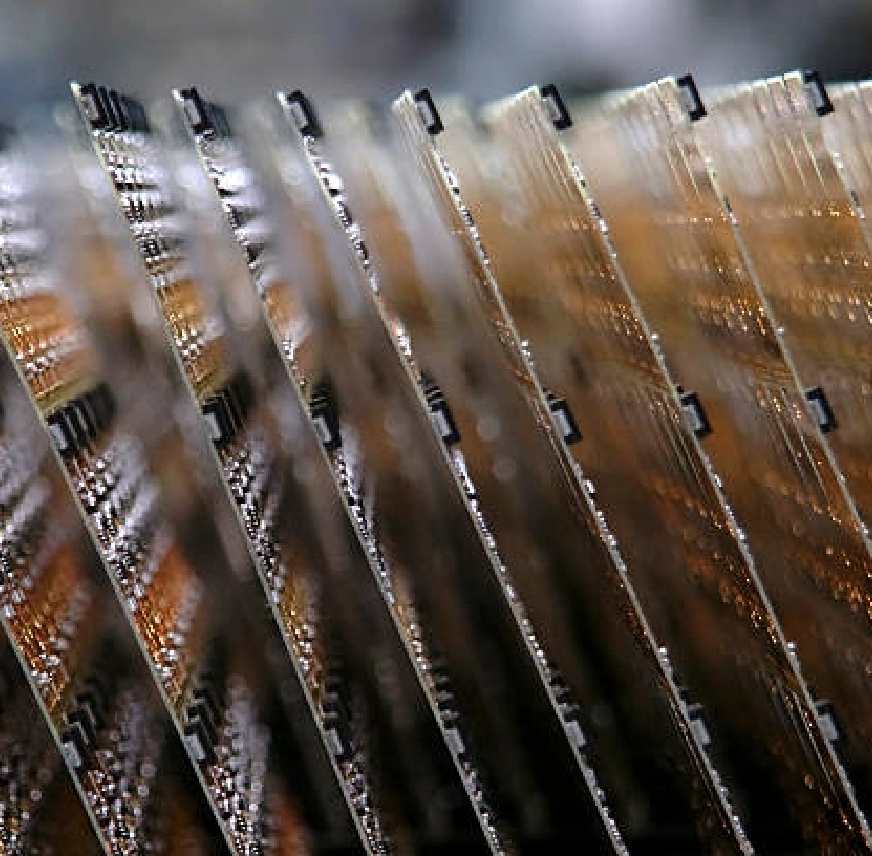

From high-speed SerDes and memory controllers to PCIe, NVMe, and UCIe integration, our silicon IP and system-level design expertise spans the full ASIC development cycle. We’ve delivered enterprise SSD controllers, stacked memory SoCs, and I/O expanders built to meet today’s most demanding technical requirements.

Analog / Mixed-Signal

Design and Layout

Our designers specialize in High-Speed TX/RX Design, SerDes, Sensor Interfaces, LDOs, Oscillatiors and Data Converters. The team has experience in multiple leading-edge technology nodes.

Robust ASIC

Design Methodology

Our ASIC design methodology enables rapid development of complex SoCs with minimal risk. Through a fully automated RTL-to-GDSII flow and rigorous verification strategies, we consistently meet aggressive PPA targets with first-pass silicon success.

Security-Driven

Silicon Design

Our security capabilities include secure processors, cryptographic IP, side-channel resistance, and secure boot flows. We operate in gov-cloud environments and deliver fully traceable, tamper-resistant designs for aerospace, defense, and mission-critical applications.

ASIC Design

Tools Expertise

We have a full suite of Cadence, Synopsys, Siemens and Ansys EDA tool flows to support customer and fab requirements.

Industries We Serve

With decades of experience on the leading edge and expertise across all disciplines, ForwardEdge is the surest path to success.

Defense

Commercial Consumer

Aerospace

Cyber

Digital Infrastructure (Edge Compute)